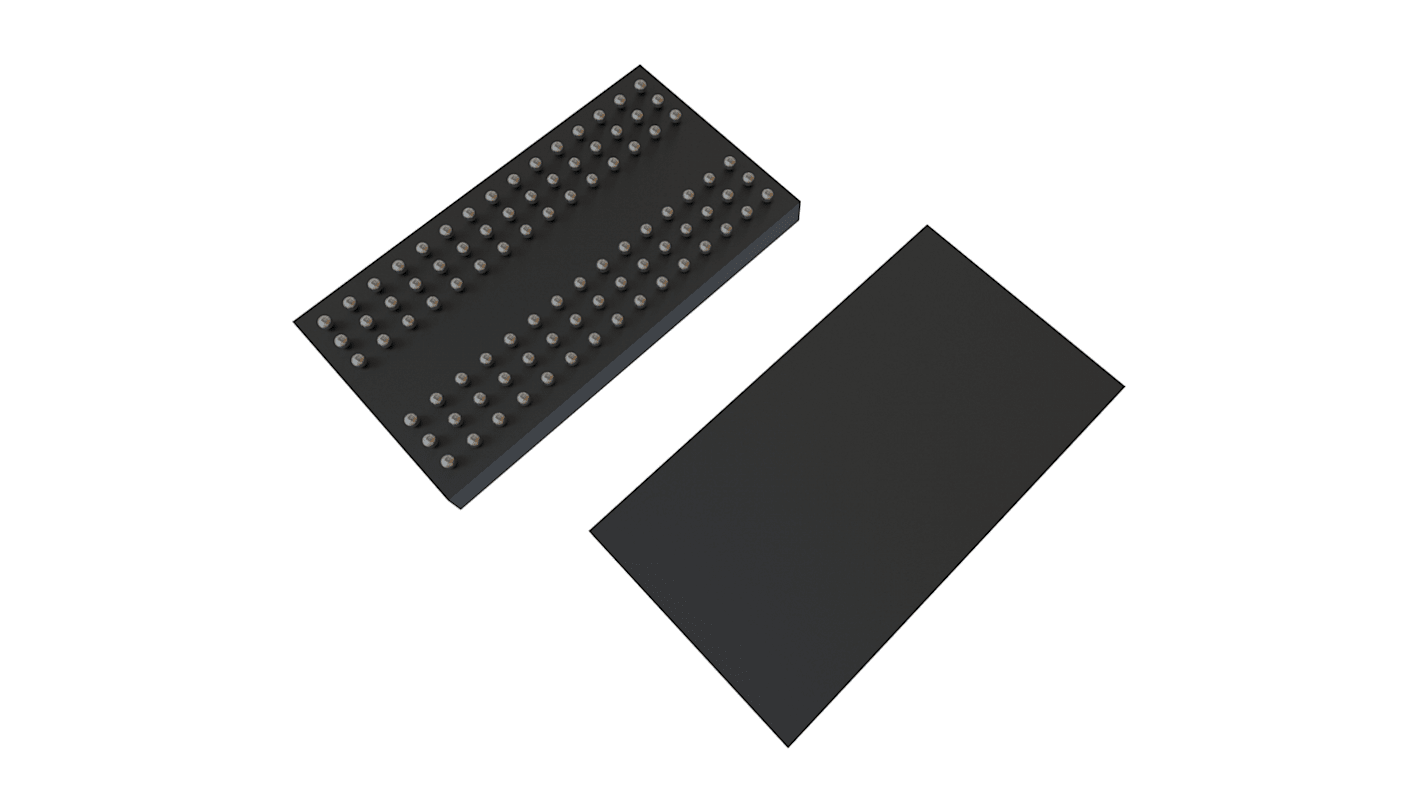

Winbond DDR2 SDRAM, 128 MB, 16 Bit数据总线, TFBGA, 84引脚, W9712G6KB系列

- RS 库存编号:

- 188-2730P

- 制造商零件编号:

- W9712G6KB25I

- 制造商:

- Winbond

可享批量折扣

小计 55 件 (按托盘提供)*

¥1,120.57

(不含税)

¥1,266.265

(含税)

暂时缺货

- 在 2026年9月24日 发货

**需要更多产品?**输入您需要的数量,点击“查看送货日期”,查看库存和送货信息。

单位 | 每单位 |

|---|---|

| 55 - 100 | RMB20.374 |

| 105 + | RMB19.936 |

* 参考价格

- RS 库存编号:

- 188-2730P

- 制造商零件编号:

- W9712G6KB25I

- 制造商:

- Winbond

产品技术参数

产品技术参数资料

法例与合规

产品详细信息

通过选择一个或多个属性来查找类似产品。

选择全部 | 属性 | 值 |

|---|---|---|

| 品牌 | Winbond | |

| 存储器大小 | 128MB | |

| 产品类型 | DDR2 SDRAM | |

| 数据总线宽度 | 16Bit | |

| 位址总线宽 | 15Bit | |

| 每字组的位元数目 | 8 | |

| 最长随机存取时间 | 0.4ns | |

| 字组数目 | 16M | |

| 安装类型 | 表面 | |

| 包装类型 | TFBGA | |

| 引脚数目 | 84 | |

| 最低工作温度 | -40°C | |

| 最高工作温度 | 95°C | |

| 长度 | 12.6mm | |

| 系列 | W9712G6KB | |

| 高度 | 0.8mm | |

| 标准/认证 | RoHS | |

| 汽车标准 | 否 | |

| 供应进气口螺纹性别 | 135mA | |

| 最低电源电压 | 1.7V | |

| 最大电源电压 | 1.9V | |

| 选择全部 | ||

|---|---|---|

品牌 Winbond | ||

存储器大小 128MB | ||

产品类型 DDR2 SDRAM | ||

数据总线宽度 16Bit | ||

位址总线宽 15Bit | ||

每字组的位元数目 8 | ||

最长随机存取时间 0.4ns | ||

字组数目 16M | ||

安装类型 表面 | ||

包装类型 TFBGA | ||

引脚数目 84 | ||

最低工作温度 -40°C | ||

最高工作温度 95°C | ||

长度 12.6mm | ||

系列 W9712G6KB | ||

高度 0.8mm | ||

标准/认证 RoHS | ||

汽车标准 否 | ||

供应进气口螺纹性别 135mA | ||

最低电源电压 1.7V | ||

最大电源电压 1.9V | ||

- COO (Country of Origin):

- TW

W9712G6KB 是 128M 位 DDR2 SDRAM,速度为 -25、25I 和 -3。

双倍数据速率架构:每个时钟周期两次数据传输

CAS 延迟:3、4、5 和 6

脉冲串长度:4 和 8

双向、差分数据选通(DQS 和 /DQS )与数据一起传输/接收。

与读取数据边缘对齐,与写入数据中心对齐

DLL 使 DQ 和 DQS 转换与时钟一致

差分时钟输入(CLK 和 /CLK)

用于写入数据的数据屏蔽 (DM)

在每个正 CLK 边沿输入的命令、数据和数据屏蔽均参考 /DQS 的两个边沿

已发布 /CAS 支持可编程添加延迟,以提高命令和数据总线效率

读取延迟 = 加法延迟加 CAS 延迟 (RL = AL + CL)

片外驱动器阻抗调整 (OCD) 和片上终端 (ODT),提高信号质量

读写脉冲串自动预充电操作

自动刷新和自刷新模式

预充电断电和主动断电

写入数据屏蔽

写入延迟 = 读取延迟 - 1 (WL = RL - 1)

接口:SSTL_18